# RSX=11M Working Design Document

Document Number: 130-951-009-03

Project Number: P2007580

Date: 17-Jun-74

Authors: M. Pellegrini, D. Cutler

COPYRIGHT 1973, DIGITAL EQUIPMENT CORP., MAYNARD, MASS.

This software is furnished to purchaser under a license for use on a single computer system and can be copied (with inclusion of DEC's copyright notice) only for use in such system, except as may otherwise be provided in writing by DEC.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

DEC assumes no responsibility for the use or reliability of its software on equipment which is not supplied by DEC.

3.0 INTERNAL STRUCTURE, PHILOSOPHY, AND FLOW OF CONTROL.

## 3.1 Introduction

In this Section we will present the internal operations of the RSX=11M Executive and the routines associated with it (drivers, and common service subroutines). Our exposition will have a tutorial slant. Section 5.0 contains a detailed description of the RSX=11M data structures. In this section we will introduce data structures on an as-needed basis, and discuss the detailed contents of these structures only where needed to render our exposition meaningful.

# 3.2 Interrupt Mechanisms

RSX=11M is a priority driven, multiprogramming, real-time operating system, and, as with any such system, its principal function is the multiplexing of sharable resources among competing tasks. multiplexing itself is made possible by the interrupt system of the hardware which causes control to be taken away from user tasks and given to the Executive. It is during this period of interrupt control that the Executive makes its decisions on granting use of shared resources. Understanding the interrupt mechanism is fundamental to understanding the Executive, and once understood, serves as a framework for describing the operation of Executive subsystems (drivers, loader, MCR, etc) and the system as a whole.

# 3.2.1 Hardware Interrupt Mechanisms - Review & Overview

The PDP=11 family of computers has two classes of interrupts:

- 1. Processor Traps, and

- 2. External Interrupts.

Processor traps are not maskable\*, that is, when they occur the processor enters the trap sequence of pushing PS and PC onto the current stack, retrieving PS and PC from the proper hardware trap vector, and, if no other interrupts are pending, initiating the processor at the location specified by the trap vector. A table of trap vectors start at location 4 and extend to location 774(8). Processor traps include\*\*:

The Maskable means that the condition can be disabled by altering the priority of the processor.

<sup>\*\*</sup> See the PDP=11 Processor Handbook for a complete list.

BPT Instruction;

EMT Instruction:

IOT Instruction:

TRAP Instruction;

11/40 Floating Point Exception Fault;

Odd address;

Power Fail, and

Illegal Instructions.

External interrupts are hardwired to one of the four bus request levels of the processor. These interrupts are generally associated with I/O devices and are maskable. They can only cause an interrupt when the priority in the Processor Status Word (PS) is less than the priority of the interrupting source. Thus, by setting the processor priority in a trap vector PS word to an appropriate level interrupts equal to, or below that priority are locked out.

Every device (interrupt source) has an associated trap vector in the vector table located in lower memory.

With this sketch of the hardware mechanism, we can examine the interrupt processing in the Executive itself.

# 3.2.2 Executive Interrupt Processing

Let us assume that all the vectors in the trap vector table have been properly initialized so that when a processor trap or interrupt occurs, an Executive routine will obtain control of the processor\*.

On a real memory PDP=11\*\*, only one stack exists, and this stack must be multiplexed to service the user tasks, the Executive, and the Executive Sub=systems.

The RSX=11M System supports n levels of user multi-programming and 250 levels of user priority. The user establishes the priority of his task and the Executive dispatches user tasks based on the highest

<sup>\* \*</sup> Section xxx.xxx describes this initialization.

parks See Section x,xxx for the details of mapped memory systems.

priority user task which is ready to run. The System Task Directory (STD), which is composed of one 18-word STD Entry (Task Control Block (TCB)) for each user task in the system, and which is ordered by priority, is scanned to dispatch user tasks.

Having only a single stack also implies a single processor state. The Executive must simulate a two state system. A single word, the stack depth indicator (SSTKDP) is used to control this simulation.

When the stack depth indicator is equal to 1 the system is running in the user state; when it's zero or less, it is in the system state. All stack multiplexing is accomplished by testing the contents of this word. In passing, we should note that the priority set in the PS word for user tasks (both privileged and unprivileged) is 0, and for Executive routines, when running interruptable, is either 0, 7 or the level at which the interrupt was taken. It is a design goal to operate the Executive and its associated routines non-interruptable for as short a duration as possible. We currently estimate the system never remains non-interruptable for more than twenty instructions with the typical span of non-interruptable codes being less than ten instructions. Furthermore, the total non-interruptable time will be less than 1/10 of 1% of the total processor time.

External interrupts can occur within the system from either of the simulated states, that is when the stack depth indicator is 1 (user state) or <=0 (system state). Processor traps, which include the EMT instruction used for Executive Directives, only occur in the user state, with the following exceptions:

TRAP Instruction

Powerfail

Describing the RSX=11M interrupt mechanism involves several interrelated routines, and it may be necessary for the reader to make two passes over this section before the process becomes completely clear. To ease your passage, we introduce now a brief description of the basic routines involved.

The RSX=11M interrupt machinery involves the following routines or routine types:

Interrupt processor (both external interrupts and traps);

The Interrupt Save Routine (\$INTSV);

The Directive Save Routine (SDIRSV);

The Interrupt Exit Routine (SINTXT);

The Directive Exit Routine (3DIRXT), and

The Fork Processors (SFORK, SFORKA, SFORK1).

Interrupt processors are entered directly and usually call \$INTSV or \$DIRSV for common save and state switching services; at the completion of these services, the interrupt routines are again given control to complete the interrupt service. The exit routines \$INTXT and \$DIRXT restore the state prior to switching to the system state, control the un=nesting of interrupts, and make checks on the state of the system (for example, is it necessary to redispatch the processor). The Fork Processors linearize access to shared system data bases. The details of all these routines will emerge in the upcoming narrative.

3.2.3 External Interrupt From The Task State (Stack Depth Indicator=1)

The vectors in lower memory contain a PC unique to each interrupting source, and a PS set with a priority of PR7. Hence, when an external interrupt occurs, the hardware pushes the current PS and PC onto the current stack (in this case the users stack) and loads the new PC and PS (set at PR7) from the appropriate interrupt vector. The interrupt routine, then starts executing with interrupts locked out, Interrupt routines may, in fact, be executing in one of three states:

- 1. At PR7 with interrupts locked out;

- 2. At the priority of the interrupting source; thus, interrupt levels greater than the source are permitted, or

- 3. At Fork level which is at PRO.

State 2 is discussed shortly; state 3 will be deferred to Section 3.2.7.2 (Fork Processes); for now, lets look at the PR7 state.

By internal convention, processing in the PR7 state (Interrupt processing state 1) is limited to 100us. If processing can be completed in this time, then the interrupt routine simply RTI's; the interrupt has been processed and dismissed with minimal overhead.

If the interrupt routine requires additional processing time (but does not intend to alter a shared system data base) it calls the routine SINTSV (Interrupt Save). The priority at which the caller is to run immediately follows the call to SINTSV.

Interrupt save uses the specified priority to set up the interrupt routine such that it is interruptable by priorities higher than that of the interrupting source (interrupt processing state 2) and conditionally switches to system state if the processor is not already in system state. The SINTSV algorithm is:

\$INTSV: Push R5 and R4 onto the current (user's) stack.

Decrement stack depth indicator

Is the stack depth indicator =0? No; go to 1

Save the current (a task's in this case) stack pointer

Set up the system stack pointer (switch stacks)

Load the new processor priority as specified by the caller

Return to caller.

#### Notesi

The Stack Depth Indicator is zero only when the transition from the user state to the system state has occurred. The user state value of 1 was selected to simplify the decrement, test, and branch which establishes whether a stack switch is necessary.

Pushing of R4 and R5 is done to free these registers for routines processing external interrupts. It is an internal programming convention that assumes these routines will not require more than two registers to accomplish their functions. If they do, they must save and restore any additional registers they use.

Example use of SINTSV\*

```

: RK11 DISK CONTROLLER INTERRUPT SERVICE ROUTINE

; THIS ROUTINE IS ENTERED VIA THE VECTOR AT LOCATION 220 WHEN AN

: INTERRUPTING CONDITION IS DETECTED IN THE RK11 CONTROLLER. THE

, ROUTINE IS ENTERED AT PRIORITY PR7 WITH ALL INTERRUPTS LOCKED OUT.

1 -

PS, TEMP

:::SAVE VECTOR PS WORD

SDKINT::MOV

SINTSV, PR5

:::SWITCH STATES AND PRIORITY TO PR5

CALL

; CONTROL IS REGAINED AT THIS POINT IN SYSTEM STATE WITH A PRIORITY OF

1 PR5. REGISTERS R4 AND R5 HAVE BEEN SAVED AND MAY BE FREELY USED.

MOV

TEMP, R4

:: RETRIEVE SAVED PS WORD

BIC

#177760.R4

;;;CLEAR ALL BUT CONTROLLER NUMBER

```

### Implementation note:

etc.

The CALL macro in the above example is a special form which is defined in the executive macro file RSXMC.MAC. This file must be concatenated with all assemblies using this form of CALL. The code generated from the macro expansion is:

JSR R5,SINTSV .WORD C<Priority>&PR7

3.2.4 External Interrupts From The System State (Stack Depth indicator <=0)

The code on this interrupt path is identical to that discussed in Section 3.2.3. However, it is not necessary to switch states when SINTSV is called. The current stack is the system stack, and the test on the value of the stack depth indicator will cause the saving of SP

<sup>\*\*\* \*</sup> We intend to make extensive use of examples throughout this manual and will repeat coding sequences where necessary to relieve the reader from continually paging to find another related example.

and the switching of stacks to be bypassed. After saving R4 and R5 on the system stack, a return to the interrupt routine is executed.

# 3.2.5 Processor Traps From The Task State (Stack Depth Indicator=1)

When a processor trap occurs from the task state, the hardware pushes PS, PC, and initiates the routine specified in the associated hardware trap vector. If the trap was an Executive directive (EMT 377), the DPB (Directive Parameter Block) or its address was pushed onto the user's stack prior to the issuance of the EMT. The trap routine, running at PR7 immediately calls the routine \$DIRSV (Directive Save) which has the following algorithm:

SDIRSV: Push R5 and R4 onto current (user's) stack

Decrement Stack depth indicator

Is the stack depth indicator #0? No, go to 1.

Save current (user's) stack pointer

Set up system stack pointer (switch stacks)

Push R3,R2,R1,RØ onto current (system) stack

Load new processor priority as specified by the caller

Return to caller.

# Notesi

The depth indicator check is made to improve crash analysis; no other decisions are made in SDIRSV since all processor traps, with two exceptions, occur from the task state. The exceptions are handled on exit. All registers are saved; the need for only two registers, R5 and R4 is assumed only for routines processing external interrupts. As with SINTSV the priority at which the caller expects to run immediately follows the call. All processor trap routines, however, run at level 0.

Only one processor trap can be queued for processing in the system at any point in time (ignore, for the moment, the two exceptions we have noted). Since the processor trap occurred in the in task state, entrance to the Executive occurs only when the Executive is idle. While in the System State, only external interrupts can occur. If processor traps occur, then either they are valid exceptions, or the system itself has faulted and will shut down.

Once a valid processor trap is pending, it will be processed to completion before any other system routine is given access to any shared system data base. We will see how this strict sequentiality is effected when we discuss the two exit routines and the fork processors.

## Example use of \$DIRSV

```

: EMT TRAP PROCESSING ROUTINE

; THIS ROUTINE IS ENTERED VIA THE VECTOR AT LOCATION 30 WHEN AN EMT

; INSTRUCTION IS EXECUTED. THE ROUTINE IS ENTERED AT PRIORITY PR7

, WITH ALL INTERRUPTS LOCKED OUT.

:::SWITCH STATES AND PRIORITY TO PRO

SEMTRP: CALL

SDIRSV, PRØ

TST

SSTKDP

!EMT EXECUTED FROM SYSTEM STATE?

BEQ

105

IF EQ NO

CRASH SYSTEM

CRASH

105:

```

# Implementation note:

etc.

The CALL macro in the above example is a special form which is defined in the executive macro file RSXMC.MAC. This file must be concatenated with all assemblies using this form of CALL. The code generated from the macro expansion is:

JSR R5, SDIRSV ... WORD TC<Priority>&PR7

#### 3.2.6 Processor Traps From The System State (Stack Level <=0)

Only two processor traps are valid from the system state: The trap instruction and powerfail. If any other processor trap occurs while in the system state, the system's operation is aborted.

# 3.2.6.1 Processing For Trap Instructions Which Occur In The System State

The trap instruction is used within the Executive as a core saving technique in returning status following the processing of an Executive Directive. The EMT 377, which is the processor trap used to initiate directives, causes entry into the Directive Dispatcher (SEMTRP) which in turn calls SDIRSV. On return from SDIRSV, but before calling the directive processing routine (and entry to the proper routine is via a CALL), the Directive Dispatcher pushes a value of +1 onto the system stack, and clears the C bit in the PS word stored on the users stack;

then it calls the proper directive processing routine to effect the directive. Figure 3.1 shows the state of the user and system stacks for both the unmapped and mapped systems at the time entry is made to the directive processing routine.

# UNMAPPED SYSTEM

| _      | USER | S STACK | _   | SYSTE | M STACE | (  |

|--------|------|---------|-----|-------|---------|----|

| 1      | (    | OPB -   | 1 1 | F     | ₹3      | ١  |

| 1      |      | 98      | 1 1 | F     | 3       | ļ  |

| 1      | ,    | °C      | 1 1 | F     | ? 1     | ļ  |

| į      |      | 25      | 1 1 | F     | ₹Ø      | ı  |

| TOS    |      | 24      | 1 1 |       |         | 11 |

| 103000 |      |         | 1   |       | N ADDR  | 1  |

# MAPPED SYSTEM

| USER'S STACK                                | SYSTEM STACK |          |     |

|---------------------------------------------|--------------|----------|-----|

| I DPB !                                     | 1            | PS       | !   |

| T O S == >= = = = = = = = = = = = = = = = = | 1            | PC       | 1   |

|                                             | 1            | R5       | 1   |

|                                             | 1            | R4       | Į   |

|                                             | 1            | R3       | 1   |

|                                             |              | R2       | 1   |

|                                             | 1            | R1       | 1   |

|                                             | ı            | RØ       | 1   |

|                                             | 1            |          | +11 |

|                                             | 1 R          | ETURN AD | R I |

#### FIGURE 3-1

The Directive processing routine now carries out its function, and in so doing is free to alter any shared system data base, since no other routine will gain access to a shared data base until the directive processing routine is completed. This arrangement of the stack and interface between the Directive Dispatcher and the Directive Processors has two advantages:

- 1. The normal return for all but a few directives is a +1 status and carry clear. This means the directive routines can return to the dispatcher with an RTS; thus the return path is one word rather than two if a JMP were employed; this scheme probably saves 100 words in the RSX=11M Executive.

- 2. Internal Executive routines can call the directive processing routines without using an EMT.

If a directive processing routine needs to return a status other than +1, and have carry clear, the routine simply replaces the +1 on the stack with the value it intends to return and then executes an RTS.

Now we come to the use of the trap instruction within the Executive, If a directive processing routine needs to return a status other than +1 and, in addition have carry set, or cleared, based on the status value returned, then it uses the trap instruction with the value of status to be returned in the low order byte of the instruction. When the trap processing routine is entered, it immediately checks for stack depth#0, and if 0, proceeds to reset the stack for correct exiting from a directive processing routine. The low order byte of the trap instruction itself overlays the +1 status currently on the stack; this value is tested and, if minus, carry is set in the user PS word, if plus, carry is left cleared. Then the exiting code of the Directive Dispatcher is entered just as if the directive processing routine had executed an RTS.

If the initial test for a stack depth indicator of  $\emptyset$  fails, then the trap processing routine calls \$DIRSV. This call is logically incorrect if the stack depth indicator was less than zero. This programming error is recognized on exit. On return from \$DIRSV, the trap processing routine checks the stack depth indicator, and if it is not zero, the system is shut down.

Note that directives are legitimate only from the task state (stack depth indicators;) so that during directive processing, the stack depth indicator is always 0. Interrupts that occur in system state disappear from the stack before the directive processing sequence resumes following an interrupt. Hence, even though the stack can grow while a directive processor is in control, this growth is transparent to the directive processor. Stating it from a different perspective, interrupts are permitted but the directive processor in control is unaware of them.

Directive processing routines thus have three methods of returning status:

- For the normal return carry clear and status equal to +1, use an RTS.

- 2. For carry clear and status other than +1, overlay the +1 status on the stack with the desired status value (status value is at 2(SP)), and RTS.

- 3. For carry clear or set, and status of one byte, use the trap instruction. This requires more overhead than 1 and 2 above but saves core, and, of course is the required return mechanism if carry is to be set.

Together, these return mechanisms from directive processing routines save between 200 and 300 words in the RSX=11M Executive as compared to returning via jump instructions.

# 3.2.6.2 Powerfall Processing

When a power failure occurs, the power failure trap processing routine is entered. This routine saves the state of the system, sets up a new power failure trap=vector PC for use when power is restored, then HALTs.

On restoration of power, the state of the system at the time the failure occurred is restored, a flag is set by software indicating that a power failure has occurred, the reschedule pointer\* is set to the null task, and the clock is re=enabled. Then, the restoration code issues an RTI, which results in the resumption of the processing that was in progress when the power failure occurred. The specific processing to reflect the occurrence of a power failure will not occur until either Directive Exit is entered or the clock interrupts. In any event, this processing is part of Directive Exit and will be discussed under Directive Exit.

Note that power failure processing is not asynchronous. As much as 1/60 of a second could elapse following restoration before the power failure is acted upon.

The records and logic needed to provide asynchronous processing are simply too large for a system with RSX=11M's core objectives. Our assumption is that asynchronous power=failure processing is not consistent with RSX=11M's objectives or markets.

# 3.2.6.3 Aborting The System

When a condition is detected that indicates the system should be shut down (crashed in an orderly manner), the detecting routine issues an IOT. The IOT processing routine, as usual, calls Directive Save, and on return checks for a stack depth equal to zero. If equal, normal SST processing is entered. If not equal to zero, the routine SCRASH is entered. Crash displays, on the device whose CSR address is CSSRSH, an appropriate printout which is detailed in Appendix I. After completing the printout, it jumps to a routine called SPANIC, which optionally prints out an edit of selected memory locations. In the minimum system both SCRASH and SPANIC are conditionalized out, and a system crash simply results in a processor halt at location 560(8).

# 3.2.7 Processing Within Interrupt Routines

In Section 3.2.2 we examined interrupt entry into the RSX=11M Executive. In this section we detail the events which take place following interrupt entry up to the point where the Executive is ready to return control to the task state.

Once the Executive is entered via an interrupt (regardless of the state its in when the interrupt occurs) it will not again return to

The reschedule pointer will be covered when we discuss task switching.

the task state until all system related processing for that interrupt has been completed. From another point of view, the task state is never in control unless the Executive has nothing-to-do (is idle).

While in the task state a single interrupt causes transfer into the system state where the system remains until the interrupt is processed. But while in the system state, repeated interrupts can occur. This implies a fixed interrupt depth of one for the task stack (requiring a task to provide a stack of at least four words in an unmapped system), and implies a variable interrupt depth for the system stack.

If interrupts can occur in the system state, then a mechanism is required to prevent unwanted recursion and improper data base modification. In RSX=11M both of these logical difficulties are resolved by strictly linearizing interrupt processing and access to internal data bases. The mechanisms employed to accomplish this linearization are the system stack, fork processes, and the associated fork list.

# 3.2.7.1 Queuing Interrupts On The System Stack

In the system state the goal is to operate interruptible as much of the time as possible. Three conditions exist when the system itself runs non-interruptable:

- The most recent interrupt is being processed at level PR7 and the interrupt routine has not yet returned to an interruptible state.

- 2. The interrupt routine has dropped from level PR7 to the level at which the interrupt occurred. Priority levels, equal to or less than the priority of the interrupting source are locked out.

- 3. The system is updating a critical list whose consistency can only be maintained by a non-interruptable instruction sequence. There are two such lists, and we will discuss them shortly.

In Sections 3.2.3 and 3.2.4 we examined the code sequence for processing external interrupts and processor traps, as well as the stack additions that occurred during their processing. Interrupt stacking in the system state will occur based principally on hardware interrupt levels. Thus if a level PR4 interrupt is being processed, then a level PR5, PR6, or PR7 interrupt can potentially interrupt this processing and cause context to be stacked and control given to the higher level interrupt routine.

## 3.2.7.2 Fork Processing And The Fork List

Once an interrupt routine passes from a non-interruptible to an interruptible state via a call to \$INTSV, processing is at the same level as the priority of the interrupting source. Along any given interrupt path however, more processing is often required than the goal of minimum non-interruptible code sequences in the Executive permits; along this path the allowable maximum non-interruptible processing time is 500us. Thus, a scheme is required to split interrupt processing routines further, such that part of their execution runs interruptible to any interrupting source. The mechanism for achieving this split is called fork processing. Fork is an internal subroutine with three entry points; fork linearizes accesses to system data bases, thus eliminating unwanted recursion and mulitple-updates of these data bases. An associated list, the Fork List, which is processed FIFO, is used as the linearizing structure.

Interrupt routines are required to adhere to the following internal conventions:

- Use of any registers except R4 and R5 requires that these registers be saved and restored.

- Non-interruptible processing must not exceed twenty instructions.

- 3. All modifications to system data bases must be done via a fork process. The first two requirements are straightforward, so lets turn our discussion to Fork.

Along an interrupt path, control can be taken from a routine only due to a higher priority interrupt pending in the hardware. As discussed previously, these interrupts are kept track of on the system stack. When an interrupt routine needs to transfer from a noninterruptible (including partial non-interruptibility) to an interruptible state, or modify a system data base, it must call Fork, Fork, however, cannot be called directly from an interrupt routine; it must first switch to system state by calling Interrupt Save and then call fork.

Fork has three entry points depending on the size of the fork block being provided by the caller for context storage.

SFORK requires a 4-word fork block which contains:

A forward link in the fork list

PC of the caller

Saved R4

Saved R5

\$FORK is for I/O drivers and the fork processor assumes R5 is loaded with the unit control block (UCB) address.

SFORK1 requires a 3-word fork block containing:

A forward link in the fork list

PC of the caller

Saved R5

SFORK@ requires a 2-word fork block containing:

A forward link in the fork list

PC of the caller

SFORK when called:

Stores the return PC, R5 and R4\* into the fork block. Appends the supplied fork block to the fork list, and jumps to Interrupt Exit.

By virture of calling fork, the routine is now interruptible and its access to system data bases is strictly linear. The interrupt processing routine is now in state 3. (Refer to Section 3.2.3 for a discussion of states 1 and 2). The Fork List is a list of system routines waiting to complete their processing, in particular, waiting to access a shared system data base.

When the Fork routine, after placing the fork block in the fork list, jumps to SINTXT the stack items for the interrupt routine are removed from the stack. In effect the fork list is a secondary interrupt queue (stack) whose members are processed FIFO, and obtain processing time only if the system stack is empty.

Note that the context saved for a caller of \$FORK depends on which entry point is called, and the context saved is all that is needed to restart routines on the fork list.

$<sup>(\</sup>gamma)$  \* R5 and R4 will or will not be stored depending on which variant of Fork is called.

## Example call to SFORK

```

; RK11 DISK CONTROLLER INTERUPT SERVICE ROUTINE

: THIS ROUTINE IS ENTERED VIA THE VECTOR AT LOCATION 220 WHEN AN

; INTERRUPTING CONDITION IS DETECTED IN THE RK11 CONTROLLER. THE

; ROUTINE IS ENTERED AT PRIORITY PR7 WITH ALL INTERRUPTS LOCKED OUT.

; -

:::SAVE VECTOR PS WORD

SDKINT::MOV

PS. TEMP

SINTSV, PR5

:::SWITCH STATES AND PRIORITY TO PRS

CALL

MOV

TEMP, R4

;;;RETRIEVE SAVED PS WORD

BIC

;;;CLEAR ALL BUT CONTROLLER NUMBER

#177760.R4

R4

111CONVERT TO WORD INDEX

ASL

CNTBL(R4),R5

MOV

:::RETRIEVE ADDRESS OF UCB

TSTB

RTTBL+1(R4)

:::DRIVE RESET IN PROGRESS?

BEQ

50$

::: IF EQ NO

drive reset processing code

50$:

CALL

SFORK

:::CREATE A FORK PROCESS

; CONTROL IS REGAINED AT THIS POINT WITH ALL INTERRUPTS ALLOWED.

```

# 3.2.8 Exiting The System State

In Section 3.2.2 = 3.2.7.2 we covered the Executive's processing of interrupts, and the methods employed to linearize their processing so as to minimize the non-interruptible time spent in the system state. In several places we referenced two routines \$INTXT (Interrupt Exit) and \$DIRXT (Directive Exit). These routines result in the sequential removal of all items on the system stack, then all items on the fork list. It is these two routines to which we now turn.

The Executive's strategic objective is to return to equilibrium (the idle state) as fast and as efficiently as possible; its tactics to achieve equilibrium is to is to service all routines on the system stack first. These routines are usually running at some level of non-interruptibility, when the system stack is cleared of pending requests, the Executive then services the pending requests on the fork list, when both the fork list and system stack are empty, the Executive will either return to the task state or if no task is active, drop into the Null Task.

TINTXT is transferred to by external interrupt processing routines that are running on the system stack at the priority of the interrupting source (state 2 for those interrupt processing routines).

\$DIRXT has the task of servicing the fork list and, when the Executive has no more work to do, restoring the task state. \$DIRXT is entered by trap routines, fork routines, and by \$INTXT.

3.2.8.1 Interrupt Exit (\$INTXT)

The \$INTXT algorithm is as follows:

SINTXT: Lock out interrupts

Is stack depth indicator#0? No, go to 1.

Is fork list empty. Yes, go to 1.

Allow interrupts.

Store R3,R2,R1,R0 on the current (system in this case) stack

jump to SDIRXT (Directive Exit).

1. Increment stack depth indicator.

Restore R4 and R5 from current stack and RTI.

#### Notesi

Interrupts must be locked out to insure a consistent check of the stack depth indicator and the contents of the fork list. The same type of lockout occurs in Directive Exit. There are two non-interruptible code spans used to check and update the fork list mentioned in Section 3.2.7.1., one in SFORK, and one in SDIRXT. The saving of R3 thru R0 is prepatory to the jump to SDIRXT which expects these registers on the stack. Note that the path through the Executive which find both the fork list empty and the stack depth indicator equal to 0 is fairly common. As can be seen, this is the minimum overhead path.

3.2.8.2 Directive Exit

The SDIRXT algorithm is as follows:

SDIRXT: Lock out interrupts.

Is the fork list empty? Yes, go to 1.

Update Fork list pointers.

Allow interrupts.

Restore Fork context.

Call routine whose fork context was restored.

Go to SDIRXT.

1. Is rescheduling required (\$RQSCH not#0)? No, go to 2.

Allow interrupts.

Clear SRQSCH.

Save context of current task.

Locate a ready-to-run task.

Restore context of new task.

Go to SDIRXT.

2. Is the power failure flag set? No, go to 3.

Allow interrupts

Call power failure processing,

Go to SDIRXT

Restore task stack pointer.

Increment stack depth indicator.

Restore R4 and R5 from user stack and RTI.

#### Notes:

SDIRXT calls both waiting fork processes and the powerfail routine. These routines terminate via a RTS instruction. On return SDIRXT again cycles looking for work.

The task reschedule pointer \$RGSCH controls the redispatching of the processor. It points to the location in the STD list where \$DIRXT should begin its scan for a task ready to use the processor.

SRQSCH is set when a change of state has occured in the system that might cause a task other than the one currently in control to obtain processor time. Examples are I/O done, clock queue runout, or a task doing an EXIT. The word is reset by SDIRXT just prior to its dispatching a new task.

# 3.2.9 Interrupt Processing Summary

Seven routines or groups of routines not only comprise the interrupt system but can be said to practically comprise the entire Executive itself.

External Interrupt Routines

Trap Routines

Interrupt Save

Directive Save

Fork and Fork Processes

Interrupt Exit

Directive Exit

External interrupts cause traps to external interrupt processing routines which run in one of three states:

- Non-interruptiple at PR7.

They run here when initially entered.

- 2. Interruptible by priorities higher than the interrupting source.

Both states 1 and 2 are linearized being queued and dequeued from the system stack.

3. Fully interruptible as fork processes.

Trap routines of which only one may occupy the system stack during any given passage through the Executive, operate at priority level zero, need never call Fork, and operate entirely from the system stack.

Interrupt save is called by external interrupt routines when they make a transition from state 1 to state 2.

Directive save is called by trap routines.

Fork creates a fork process for external interrupt routines.

Interrupt Exit unstacks waiting routines executing from the system stack, and when the system stack is empty drops into Directive Exit.

Directive Exit has the job of giving control to waiting fork processes, processing power failure, and redispatching the processor.

The Executive structure has an implied sequentiality which obviates the need for any explicit synchronizing mechanisms. System routines which follow the internal conventions of the Executive never need concern themselves with multiple-update of shared system data bases. In tending toward the idle state the Executive gives priority to routines on the system stack, then to fork processes.

# 3.3 I/O Processing

## 3.3.1 Goals

The I/O interface is 100% compatible with RSX=11D. Within the requirement of compatibility, three goals guided the design:

- 1. The total memory for I/O processing (data structures plus drivers) must be reduced by 50% vs RSX=11D.

- 2. The I/O data structures should have substantial flexibility for adding future devices, or for altering the service discipline of existing devices.

- 3. Throughput should equal or exceed RSX=11D's.

# 3.3.2 I/O Philosophy and Functional Overview Of Its Implementation

To meet its stated goals, the RSX-11M I/O system attempts to centralize common functions, thus eliminating the repetitive oppearance of code, which is almost identical in form and function, from appearing in each and every driver in the system. To achieve this, a substantial effort has been expended in the design of RSX-11M's I/O data structures which are used to drive the centralized routines. The effect is to substantially reduce the size of individual I/O drivers; an RSX=11M driver is typically one-fourth as large as its RSX=11D counterpart. Of course, the centralized code, and an increase in the size of RSX=11M's data structures compared to RSX=11D's reduces our effective size reduction. But, on the balance, we have substantially reduced the size of our total I/O processing core requirements while at the same time produced a more understandable, maintainable, and enhanceable I/O system (obviously, our subjective judgement).

The user interface to the RSX=11M I/O system consists of logical unit numbers (LUNs) and a single active I/O directive QUEUE I/O. (The directives ASSIGN LUN, GET LUN INFO, etc. do not initiate I/O transfers).

In RSX=11M all the preliminary processing antecedent to actually queuing an I/O request is performed by the QIO directive processing code which is driven from the I/O data structures; this code calls ancillary routines for centralized services. When a driver finally receives an I/O order, it has very little to do other than set up the status registers and issue the order.

Termination processing is equally modular and centralized. The driver is entered, performs some cleanup operations, and calls centralized routines for obtaining pending I/O orders, performing AST processing,

etc. The driver is only concerned with the most intimate and specific details of the actual hardware interface in respect to the execution and completion of I/O transfers. Using this centralization philosophy, RSX=11M keeps both driver size and non-interruptible processing time small.

## 3.3.3 RSX=11M I/O Data Structures

The static\* I/O data structures consists of three distinct entities:

- 1. A Device Control Block (DCB):

- 2. A Unit Control Block (UCB), and

- 3. A Status Control Block (SCB).

Although each serves a specific function, and the components of each, in general, reflect these functions, the coherence achieved by a strict set of rules for determining into which data structure a specific unit of information would be placed was ultimately sacrificed to core savings and code efficiency. The exceptions, however, are few, and the functional purpose of each data structure is reflected by the units of information which compose them.

# 3.3.3.1 The Device Control Block (DCB)

One device control block exists for each device type attached to the system. Its function is to describe the static characteristics of both the controller and the units attached to the controller. All the DCB's in the system are singly linked. The DCB contains such information as:

The device mnemonic (Two ASCII characters)

The lowest and highest Unit Numbers on the respective Controller

The address of the first UCB

The Length of Each UCB

The next DCB Pointer

The Legal Function Mask

<sup>\*</sup> Static in the sense that they are established at SYSGEN and only another SYSGEN can expand or contract the number of I/O units served by the structures.

The Control Function Mask

The No-Op'd Function Mask

The File Function Mask

The Pointer to the Driver Dispatch Table

All these information units are static and are used principally by the QUEUE I/O directive processing code to prepare a Queue I/O request for a device driver. The details of QUEUE I/O Processing are in Section 3.3.5.

# 3.3.3.2 The Unit Control Block (UCB).

One unit control block exists for each physical device unit attached to the system. Many of its information units are static, though it does contain a few dynamic parameters. For example the redirect pointer which reflects the result of a Redirect MCR command.

The UCB contains device unit specific data, such as unit status, physical unit number, and unit characteristics.

## 3.3.3.3 The Status Control Block (SCB).

One status control block exists for each device controller in the system. This is true even if the controller handles more than one device unit (like the RK Controller). Line multiplexers such as the DH11 and DJ11 are considered to have a controller per line since all lines may transfer in parallel.

Most information in the SCB is dynamic. It contains the following information about the currently active unit:

The Interrupt Vector Address

The Controller Bus Request Priority

Timeout Counts (Initial and Current)

The Address of the Control Status Register

The Address of the Current I/O Packet

Storage For A Fork Block

The I/O Queue Listhead

The Controller Status (Busy/Idle)

The Controller Index

As can be seen, the SCB is quite dynamic, making it possible to maintain control of the current I/O in progress on the controller. The presence of the fork block storage in the SCB implies I/O linearity for the processing at fork level on a given controller. We have here a specific example of how multiple updates and recursion are controlled. The driver for a specific device type never concerns itself with unwanted recursion or multiple updates. Once a driver is in a fork level process, further I/O processing, which may involve updating a shared data base, is automatically locked out by the structure of the system itself.

## 3.3.4 Some Sample I/O Structures

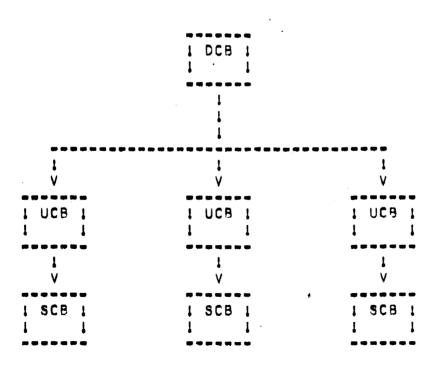

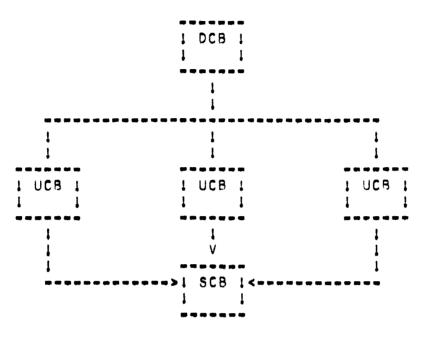

Figure 3-2 shows the data structure that would result for three terminals each interfaced via a DL11 asynchronous line interface. The structure requires three UCBs and three SCBs since the activity on all three units can proceed in parallel. In Figure 3-3 the internal data structure for an RK disk controller with three units is depicted; note that only one SCB exists because only one of the three units may be active at any time.

FIGURE 3-2

Figure 3-3

# 3.3.5 Queue I/O Directive Flow

The Queue I/O directive requires the issuer to construct a twelve word directive parameter block as shown in Figure 3-4.

| 1 | LENGTH ! DIC            |      |

|---|-------------------------|------|

| 1 | FUNCT CODE   MODIF      | ER ! |

| 1 | RESERVED ! LUN          | 1    |

| 1 | PRIORITY   EFN          | 1    |

| 1 | I/O STATUS BLOCK ADDRES | 3S ! |

| ! | AST ADDRESS             | 1    |

| ! | DEVICE                  | !    |

| 1 | DEPENDENT               | 1    |

| 1 | PARAMETERS              | 1    |

| 1 |                         | 1    |

| 1 |                         | 1    |

| 1 |                         |      |

Figure 3-4

The parameters have the following interpretation.

Length (required):

The length of DPB. For QIO always equal to twelve words.

DIC (required):

Directive Identification Code. For QIO, the value is a 1.

Function Code (required):

The code of the requested I/O function (Ø thru 31.).

Modifier:

Device dependent modifier bits.

Reserved:

Reserved byte and must not be used.

LUN (required):

Logical Unit Number.

Priority:

Request priority. Ignored by RSX=11M, but space must be allocated for RSX=11D compatibility.

EFN (optional):

Event flag number.

I/O Status Block Address (optional):

This word contains a pointer to the I/O status block which is a 4-byte device dependent I/O completion data packet formatted as:

Byte @

I/O status byte

Byte 1

Augmented data supplied by the driver

Bytes 2 and 3

The contents of these bytes depend on the value of byte  $\emptyset$ . If byte  $\emptyset$ =1 then these bytes contain the processed byte count. If not=1, then the contents are device dependent,

AST Address (optional):

Address of an AST Service Routine.

Device Dependent Parameters:

Up to six parameters specific to the device. Typically these are:

Buffer address

Byte count

Carriage control type

Logical block number

Any optional parameters that are not specified must be filled with zeros.

When the QIO directive is issued, QIO directive processing code receives control and processes the request as follows:

1. [Perform first level validity checks]

QIO examines the LUT (Logical Unit Table) in the task header for a LUN match.

It checks if the LUN is legal for the requesting task. If the LUN is greater than the available LUT slots established for the task the directive is rejected. Given a valid LUN, a check is made to determine if a valid UCB pointer exists in the LUT for the specified LUN. If none exists the directive is rejected. If the LUN and UCB pointer are valid, the redirect algorithm is entered.

1a. [Redirect algorithm]

The UCB is located and the re-direct pointer checked. If the re-direct pointer points to the UCB which contains it, then the final link in the redirect chain has been found. the redirect UCB address is obtained and the test is repeated. This search continues until the last re-directed UCB is found. Then, the backpointer to the DCB is used to locate the DCB and a check on the device name is made. the name is TI, then the address of the UCB which is to be used to control I/O transfers is in the TCB of the requesting task. This pointer was implanted by MCR when it requested the task and the chaining process described links the requesting task to the terminal which requested it. If the name is not II, the final UCB in the redirect chain is used for the I/O Transfer. The EFN and I/O status block (IOSB) address are validated and the priority is ignored. If any of these checks fail, the directive is rejected. If the checks pass, the directive status is set to +1 and the IOSB, if specified, is cleared.

2. [Obtain storage for, and create an I/O driver queue entry]

After the first level checks prove positive, QIO obtains an 18-word storage block from dynamic storage. Into this block, which we will refer to as an I/O packet, QIO inserts the following (the source of the data is specified with each data item)

Function Code

Copied from the DPB

Contents of the first LUN word Established by the redirect algorithm

Address of the second LUN word Calculated from the requesting task's header address

EFN Copied from the DPB

Priority

Copied from TCB of the requesting task

Address of the Task Control Block

The TCB address of the requesting task

Virtual address of the I/O status block Copied from the DPB

Relocation Bias of the I/O status block\* Calculated

Address of the I/O status block\* Calculated

AST address

Copied from the DPB

Device Dependent Parameters

Copied from the DPR

3. [Validate the function request]

Using the legal-function mask in the DCB, QIO determines if the requested function is legal. If it is not legal, go to 9.

4. [Check for no-op'ed function]

Using the no-op'ed function mask in the DCB, check if the requested function is to be no-op'ed. If yes, go to 9.

5. [Check for a Control Function]

Using the control function mask in the DCB, determine if the requested function is a control function. If yes, go to 8.

Check for a file system function!

The next tier of function checks determine if the function is a file system function. If it is, a check is made to see whether the device to which the request is directed is file structured. If it is we go to 8. If the device is not file structured, then the function requested must be either a read virtual or write virtual. The request is mapped to its logical counterpart (read or write logical) and processing proceeds at step 7.

These exist to satisfy requirements of the mapped system. A separate section will detail the differences between a mapped and unmapped system.

7. [Transfer function processing]

If the function is legal, but not a nomop or control function, then it's a transfer function, and address checks are made on the buffer, count, and modulus requirements. If any of these fail, go to 9.

8. [Packet Queuing]

QIO checks the control bits in the UCB which determines if it will queue the packet and then call the driver, or call the driver and let the driver queue the packet. The call to the driver is via the pointer in the DCB to the driver dispatch table entry addresses, namely:

INITIATOR

CANCEL I/O

POWER FAILURE

DEVICE TIMEOUT.

In this case the initiator entry point is called, and normal path QIO directive processing is complete.

9. [Function is illegal, no-opfed, or invalid parameters]

If any of these cases pertain, QIO calls I/O Done and passes a status code. A special entry point is used which causes I/O Done to bypass clearing of the unit and controller busy flags, clearing of which occurs along I/O Done's normal path.

#### Notes:

By reviewing the algorithm for the QIO directive processing, the reader should note the care taken to relieve the driver of validation processing. It's through the centralization of validation processing that driver code is substantially shortened and structurally simplified. A beneficial fallout of this strategy is that drivers are not called with requests that are going to either fail on a premissue validation check, or not result in the issuance of an actual I/O (like no-op and control functions). This substantially reduces internal overhead.

3.3.6 Issuing I/O

<sup>\*</sup> Modulus checks exist for devices which have boundary alignment requirements.

QIO calls the driver at the initiation entry point. We will avoid the subtlety of when packet queuing does not occur and assume it's queued. The driver algorithm is as follows:

## 1. [Get an I/O request]

When the driver is called, it immediately calls the internal routine Get Packet (SGTPKT). Get Packet is discussed in Section 3.3.6.1. SGTPKT either delivers a packet, or returns busy. If busy, go to 3.

# 2. [I/O Issue]

The driver builds the actual I/O order and issues it. It then returns, in this case to QIO. QIO returns the directive status to the user issuing the original QIO directive and clears the directive from the stack by returning to the directive dispatcher.

# 3. [GTPKT returns busy]

If SGTPKT finds the controller busy, thus making it unable to return an I/O packet to the driver, it simply returns a busy indication. The busy indication simply informs the driver that it cannot at this time issue an I/O order. The driver returns to QIO, which returns the directive status to the user issuing the original QIO directive and clears the directive from the stack by returning to the directive dispatcher. The original I/O is in the driver queue, and the issuer can take appropriate action (waitfor or continue).

# 3.3.6.1 Get Packet Routine

Get Packet (\$GTPKT) is called when an I/O driver needs work. This occurs following a QIO call on the driver, and after a driver has processed an I/O termination. \$GTPKT does not know about the initiation cause of a call upon it, it simply attempts to find work for the driver and proceeds as follows:

# 1. [Scan the driver Q]

SGTPKT is passed a UCB address, which it uses to locate the SCB and the I/O queue. If the controller is busy, \$GTPKT returns busy to the caller. If the controller is free, a queue scan is begun for the highest priority request that the driver can initiate. Note that the queue is already in priority order and the question to be resolved is whether an entry represents work the driver can do. Also note, that if a controller is free, all units on the controller are free. Each queue entry must be checked to determine if the unit to which it is directed is attached. If it is attached, \$GTPKT

must check if the attached task is the same as requesting task. If it is, it returns the packet to the driver. If it is not, it continues the queue scan. It will either find work, or return busy.

## 3.3.7 Termination Processing

On an I/O interrupt (specifically a termination in our present discussion) the driver is entered directly. The driver first calls SINTSV and then SFORK. Or return from SFORK access to shared data bases has been linearized and the driver may finish processing of the I/O request. The routine that performs this processing is called I/O done.

#### I/O Done proceeds as follows:

The controller and unit are unbusied. (Both the controller and unit require busy indicators to enable the Executive to identify the controller-unit busy relationship if a power failure occurs).

The relocation bias and IOSB address in the I/O packet are used to locate the IOSB. If an IOSB was specified then the final status is stored. I/O Done then decrements the outstanding I/O count (the I/O Count is used to prevent task checkpointing if outstanding I/O's are pending for the task). If the count goes to zero, and the task was blocked for I/O rundown, the task is unblocked.

If a checkpoint request was pending for the task, an internal routine is called that will initiate the checkpointing process.

A check is then made to determine if an AST address was specified, if not, the  $I/\dot{O}$  packet is released to dynamic storage, a significant event is declared, and I/O Done returns to the driver.

If an AST address was specified, the I/O packet is used for the required AST dynamic storage and it is linked into the AST listhead for the task. A significant event is declared and I/O Done then returns to the driver. On return, the driver will jump to its initiator entry point with the address of the just unbusied device UCB in R5. The initiator calls \$GTPKT and the process of looking for work begins again. It should be noted that once underway, either by a call from QIO, or entry from an interrupt termination, a driver propagates its own execution by cycling back to its initiator entry point looking for more work.

# 3.3.8 I/O Processing Summary

RSX=11M I/O drives itself from four data structures:

The Device Control Blocks

The Unit Control Blocks

The Status Control Block, and

The 18-word driver queue I/O packet.

Centralized routines facilitate both initiation and termination processing. And, finally, the fork structures used by the drivers along paths requiring more than 500us of processing both linearize access to the I/O data bases, and decrease the non-interruptible time within the system itself.

#### 3.4 MCR - Monitor Console Routine

MCR is the collection of functions that make it possible to operate and control the RSX=11<sup>M</sup> system from a terminal device. As the link between the collection of services provided by RSX=11<sup>M</sup> and users who want to make use of these services, MCR provides a number of services, specifically:

Services 1-16 run as MCR overlays.

#### 1. ABOrt

The task name submitted with the command will be aborted.

#### 2. ALTer

The priority of the named task is altered.

#### 3. CANCEL

Periodic rescheduling is terminated for task name submitted. The task itself remains in the STD, and may be active or inactive.

#### 4. DEVices

Symbolic names of all devices known to the system are displayed on the requesting terminal. The display includes any device redirections.

#### 5. FIX

The named task is fixed in memory. This task cannot be checkpointed, and will remain in memory at task exit.

# 6. LUN

A list of Logical Unit Numbers and their associated device symbolics is displayed for the task name submitted with the command.

#### 7. OPen

Open is used for examination and/or modification of main memory.

#### 8. PARtitions

This command outputs a description of each partition and sub-partition in the system. The list also specifies if the partition is a task or common partition.

## 9. REAsign

Reassign de-assigns a Logical Unit Number from one physical device and assigning it to another for the named task.

## 10. REDirect

Redirect makes posible the redirecting of all I/O requests from one physical device to another having compatible characteristics.

#### 11. REMove

The task named is deleted from the STD. The task so removed is unknown to the Executive and exists only as a disk image.

## 12. RUN

This command enables a task to be scheduled in terms of:

- a. A delta time from now, or

- b. A delta time from clock unit synchronization, or

- c. Absolute time of day, or

- d. Immediate execution.

with options a, b, and c periodic rescheduling is provided.

## 13. SAVe

This command preserves an image of the RSX-11M Executive on disk such that a hardware bootstrap or the BOOt MCR function can reload and start up the system.

# 14. SET

Set terminal and device parameters.

## 15. TASKS

This command outputs a description of every task which exists in the STD.

## 16. UNFfx

Unfix reverses the effect of FIX.

Services 17-22 run as tasks.

17. BOOt

The Boot Command will bootstrap an RSX=11M system from a file that was either created by the SYSGEN process or the SAV MCR function.

18. DMOunt

Declares a volume logically off-line.

19. INItialize

Creates an RSX-11M structured volume.

20. INStall

The task contained in the file specified in the command is entered into the STD, and the task header is initialized.

21. MOUnt

Declares a volume logically on-line.

22. UFD

This command creates a User File Directory (UFD) and enters its name into the Master File Directory (MFD).

#### 3.4.1 Structure And Operational Environment Of MCR

MCR is an RSX=11M task which operates out of a subpartition which is part of a main partition occupied by the File System\*. TKTN, the task termination notification task, also operates out of a subpartition of the File System partition. The partition is set up so that the file system is checkpointable and either TKTN or MCR can checkpoint the File System. Thus, the file system will be swapped out and MCR swapped in when an operator request occurs.

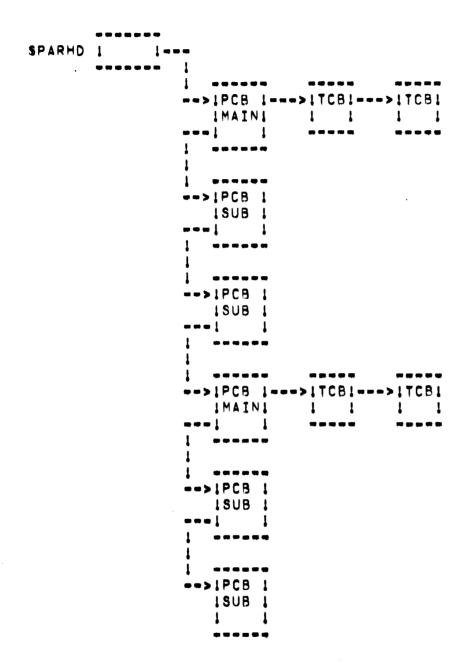

MCR is a tree structured task, and its structure is depicted schematically in Figure 3=5.

<sup>\*</sup> We mean that part of the file system referred to as File Control Primitives.

|            |       |       |     | 1<br>1<br>1<br>000T<br>1 |         |            |    |      |

|------------|-------|-------|-----|--------------------------|---------|------------|----|------|

| <br>       | 1     | 1     | 1   | 1 1<br>1 1               | 1       |            | 1  | <br> |

| DISPATCHER | PARSE | RS (1 | -3) | COMMAND                  | FUNCTIO | N PROCESSO | RS | i    |

| 1          | 1     | 1     | 1   | 1 1                      | ı       | 1          | 1  | 1    |

| 1          | 1     | 1     | 1   | 1 1                      | 1       | 1          | 1  | 1    |

| _          | _     | _     | _   |                          | _       | -          | _  | _    |

Figure 3=5 MCR Tree Structure

The command function processors are those that process the first 16 console services listed in Section 3.4. The remaining console services run as tasks and not as integral parts of MCR. MCR, in fact, does not distinguish between these task functions, and tasks that it initiates as a result of recognizing an MCR request for functions 17-22 listed in Section 3.4. The console language syntax is defined such that if the first three characters of an input line are not part of the defined command language, then MCR will attempt to initiate the task named

...XXX

Thus, the task named ... JIM can be initiated by entering

JIM

to MCR, or by entering

RUN ...JIM

to MCR.

# 3.4.2 The Terminal Driver and MCR Initiation

The terminal driver is intimately integrated into the operation of MCR. Since RSX=11M accepts and acts upon unsolicited input from any operator terminal, it is the function of the terminal driver to know when it is receiving input destined for MCR.

When a character on an operator terminal is struck, the resulting interrupt initiates the terminal driver. (Remember the device is full duplex and the keyboard cannot be locked to prevent input when the

device is, in fact, involved in an I/O operation). The driver then acts on the input as follows.

## 1. [Check the device state]

Is, the device busy. No, go to 3.

## 2. [The device is busy]

If the driver was sending output (in an output state) when the character was entered, an input request flag is set in the appropriate UCB and the driver continues sending the output stream. When the output request is finished, processing continues at 5.

If the terminal was in an input state the character is accepted. Go to 6.

#### 3. [Device is not busy]

Note, if the device was not busy, the incoming character is the first character of an input line.

Was the input character a Control=C? (Control=C is an explicit request to communicate with MCR). If the character was a Control=C, the terminal driver executes a fork and execution continues at 4.

If the first character is not a Control=C, then a check is made to see if the device is attached. If yes, then ignore the character (unsolicited input to MCR on an attached device is not permitted).

If the device is unattached then it will be considered the beginning of unsolicited input to MCR. Go to 4.

#### 4. [Fork level processing]

The driver has transferred to fork level because it needs a buffer, and it can only get a buffer at fork level (shared system tables must be altered to obtain a buffer). In addition to getting a buffer, the fork level terminal processing code must check for a rare race condition.

After the arrival of the Control=C (or a non Control=C character if the terminal is not attached) and between the time the fork is executed and control is regained in the driver, it is possible that the device may have returned to the busy state. This is because we may have just unbusied the device for a previous request when the input interrupt occurred. The interrupt code finds the device free and executes a fork. But before control is regained at fork level, execution is continued in the driver for the previous

request. The driver jumps to the initiator entry to propagate its execution and thus may find another waiting I/O request which it will begin processing since the device is free. Thus the fork routine must recheck the state of the device. If it is busy the input is ignored and the driver returns (exits) from fork level. Else an attempt is made to obtain a buffer for the unsolicited input.

# 5. [Buffer Acquisition]

If the buffer acquisition attempt is unsuccessful, the driver ignores the input and exits.

If a buffer is obtained, the driver sets up to start an unsolicited input request by initializing various pointers and setting the status of the controller and unit to busy.

If the initial input character was Control-C, then

MCR>

is echoed to signify an explicit request to input to MCR.

Else the input character is stored in the buffer and echoed on the initiating terminal.

The driver returns (exits) from fork level.

#### (Character processing)

Once the terminal driver has determined that input coming from an operator terminal is destined for MCR, it will transfer subsequent characters into the buffer acquired in Step 5. It also echoes the incoming characters. The acceptance of input will cease if:

a. The buffer is filled (the buffer has room for 80 characters) but the maximum accepted depends on the device:

72 for KSR

72 FOR VTØ5B

80 for LA305

80 for LA30S

b. An end of line character is entered. The valid end of line characters are:

Control-Z

#### Carriage Return

ALT-Mode (codes 33, 175, and 176)

#### 7. [Interrupt from a character echo]

Is the device in input mode? If no go get another character from the user output buffer and echo it. If the device is in input mode, is end=of=line set? If no re=enable the keyboard interrupt and exit from the interrupt. If end=of=line is detected, then fork.

## 8. [End-of-line processing - fork level]

Was the input solicited or unsolicited? For unsolicited input, deposit the UCB address and the terminating character into the input buffer and link the buffer into MCR's input queue, then request MCR to run. The driver itself clears control and unit busy and returns to its initiator entry point.

For solicited input I/O Done will be called. First, the number of characters entered is determined and the buffered input is moved to the soliciting task's input buffer. The driver input buffer is released and I/O Done is called with the second I/O status word equal to the number of bytes entered. The left byte of the first I/O status word is set equal to the terminating character and the right byte to +1. The driver then jumps to the initiator entry point to propagate its execution.

## 3.4.3 MCR Operation

After the request of MCR by the driver, the file system is swapped out and MCR is swapped in. Control is passed to the MCR root segment which calls the Dispatcher (DSPTCH) overlay. DSPTCH, via a privileged subroutine (\$SWSTK), switches to system state. The call to this routine includes a parameter which is the address where the caller wants to return when it switches back to task state. The state switching routine performs the switch and resumes processing in the caller immediately following the call. When \$SWSTK is called, it sets up an interrupt entry to the system. Interrupts are locked out while it pushes the passed return address and the PS on the stack. \$SWSTK then calls interrupt save (\$INTSV). On return from interrupt save R3, R2, R1, R0 are pushed onto the stack and now the stack state simulates that of an EMT. \$SWSTK now calls the caller who resumes execution one instruction past the call. When the calling routine finishes, it returns, which takes it back to \$SWSTK. \$SWSTK Jumps to Directive Exit which redispatches the processor. The effect of this is to resume the caller in task state at the passed return address.

## MCR now proceeds as follows:

#### 1. [Request an unsolicited input queue entry]

The Dispatcher cails the Queue Removal routine (\$QRMVF). \$QRMVF will attempt to remove a buffer and deliver it to the Dispatcher. If no buffer is available (carry set return from \$QRMVF) the Dispatcher exits. The buffer is formatted as shown in Figure 3-6.

| <word><word< th=""><th></th></word<></word>    |  |

|------------------------------------------------|--|

| ! LINK TO ! UCB OF<br>! NEXT BUFFER! INPUT DEV |  |

|                                                |  |

Figure 3-6 Input Buffer

The queue empty condition will never occur on an initial call to MCR, since MCR is not requested unless something is in the queue. MCR will remain resident until it has processed all the entries in the unsolicited input queue.

Note that the Dispatcher, during buffer requisition, is operating at system level, and all queue entries are done at fork level. Thus the buffer removal process is linearized with buffer item entry.

If DSPTCH gets a buffer, it saves the buffer address in a memory location and does a return. This return takes DSPTCH back to task state where the processing of the buffer begins.

## 2. [Process a [Buffer]

On return to task state, the dispatcher scans through the buffer and

compresses out redundant spaces and/or tabs converts an Escape character to a Carriage return truncates trailing spaces and/or tabs

If no line terminator is found in the buffer, a CR is inserted as the 80th character. Finally the actual line terminator (either CR or ESC) is saved so it can be restored in the message if the message must be routed to a task other than MCR itself.

The dispatcher then converts the first three characters to RAD50 and begins to search two internal tables for an MCR function with a matching name.

#### 3. [Searching the function tables - Table descriptions]

MCR has two function tables; one for privileged commands, and one for non-privileged commands.

Privileged commands are those whose unrestricted use could cause privacy violation or system failures and they can only be executed from a privileged terminal. Privileged terminals are identified by a bit in the UCB. These terminals are established at SYSGEN or by the SET command.

Both tables contain a 5-word packet for each command in the class (privileged or non-privileged). The packet appears in Figure 3-7.

|   |     |   |   |   |   |   | - |   |   | • |   | - |              |   | • |   | - | _ |   | _ |   |     |   |   |   |   |        |   |   |   |

|---|-----|---|---|---|---|---|---|---|---|---|---|---|--------------|---|---|---|---|---|---|---|---|-----|---|---|---|---|--------|---|---|---|

| 1 |     | _ | R | A | D | 5 | Ø | _ | C | M | D | _ | N            | A | M | E | _ | ( | 3 | _ | C | H   | A | R | 5 | ) | _      |   |   | 1 |

| 1 |     | I | N | D | E | X | _ | I | N | T | 0 | _ | C            | 0 | M | M | A | N | D | _ | 0 | V   | E | R | L | A | -<br>Y |   |   | 1 |

| 1 |     | _ | _ | A | D | D | R | E | S | 5 | _ | 0 | F            | _ | P | A | R | S | E | R | _ | T   | A | B | L | Ε | _      |   |   | 1 |

| 1 |     | _ | R | A | D | 5 | 0 | _ | C | 0 | M | M | 0            | N | - | 0 | ٧ | E | R | L | A | Y   | _ | N | A | M | E      |   |   | 1 |

| 1 |     | _ | I | N | 0 | E | X | _ | I | N | T | 0 | <del>-</del> | C | 0 | M | M | 0 | N | _ | 0 | V - | E | R | L | A | Y      |   |   | 1 |

| - | ~ ~ | - | - |   | - | • |   | - | _ | - | _ | • | ~            | - | • | • | _ | • | • | • | • | •   | • | - | - | • |        | • | - | - |

Figure 3-7 - Function Table Entry

The table is designed with the assumption that a given MCR function would not require more than three overlays to carry out its intent. Thus, the table entries correspond to three overlay types:

Command overlay.

Parser overlay, and

Common overlay.

The use of these overlay types is in general observed, but exceptions occur and they will be noted.

Typically, any command that can be processed in a single overlay, and whose size is such that it requires all or nearly all of the max overlay size (600 wds) will be classed as a command overlay.

Parsers for the commands are distinct entities and are grouped into overlays. Generally, a given parser services more than one command but three parsers currently service all

the commands. The parser entry is a pointer to a parser table entry shown in Figure 3-8.

1 RAD50 PARSER NAME (3-CHARS) 1 1 INDEX INTO PARSER OVERLAY 1

Figure 3-8 - Parser Table Entry

Since three parsers service all the commands it is more economical in storage space to point to the parser table rather than include the name and the index in the main function table.

The index is used as the entry point into the parser where the parsing for a given command begins. This is required since a parser can, and generally does, contain parsers for more than one command.

The common overlay is used when the processing for a command is small enough to make it practical to group more than one command into a single overlay. This grouping saves space since ten words are required by the Overlay Runtime System for each overlay in a tree structure. The Index serves the same purpose as the index in a parser overlay.

Note that a command overlay also contains an index. The value of the command overlay index is generally zero. But to maintain the coherence of the table processing commonality, and to allow for flexibility, the index is included.

3a. [Look up and start a function other than an MCR internal function]

The dispatcher then looks in the <u>privileged command table</u> for a mame which matches the first three characters in the input buffer. This table contains all the privileged MCR commands. These are noted in the commands listed in Section 3.4.1.

Internally, privileged terminals are identified by a bit in the UCB. The bit is set at SYSGEN or from a privileged terminal using the SET MCR command.

If the command is not found in the privileged command table, the non-privileged command table is searched.

If the name is not in either table, then the dispatcher will prefix three periods to the three buffer characters and using these six characters will search the STD looking for a match

on the name. If it does not find the name it will display an error message on the initiating terminal. If it finds the name, it will request the function to run, supplying as an argument to the requested task the UCB address that was in the input buffer. The UCB address is inserted into the TCB of the requested task as its TI (terminal input) pseudo device. If the attempt to request the task fails an error message is displayed, the buffer is released and MCR exits. Having discovered a non-internal MCR function, MCR must prepare to pass the buffer, since the initiated task is going to issue a GET MCR COMMAND LINE directive. To pass the buffer MCR uses three words in System Common. These words are:

- The TCB address of the requested task;

- 2. The address of the command buffer, and

- 3. The byte count of the number of input characters in the buffer.

MCR fills these words, making synchronizing checks that they are free, since only one triplet exists for passing buffers to a requested task. Thus, until the buffer is emptied, other completed buffers in the queue will be waiting.

Eventually (and this should be soon) the requested task will start running, and issue a GET MCR COMMAND LINE directive. The directive processing then tests for a match on the TCB address in SYSCM and the TCB address of the requesting task. If they match the buffer is passed to the task by copying it into the DPB of the directive. The directive status is set to the byte count, the buffer is released and the TCB address in the SYSCM triplet is cleared. The TCB address being zero is an indication to MCR that the triplet is free.

3b. [Start an internal MCR function]

Once a name match has been found in the command table, the Dispatcher copies words 1, 2, 4 and 5 of the function table entry and both words of the parser table entry for this command into the MCR root segment. Now the Dispatcher scans the function table entry as follows:

3c. IF

A parser exists

THEN

Go to 4

ELSE

IF

a command overlay exists

THEN

Go to 3d

ELSE

ΙF

a common overlay exists

THEN

Go to 5

ELSE

Abort

3d. Form overlay name, construct required overlay information packet, and enter the root at the point where overlay loading is performed.

## 4. [Parser functions]

The selected parser will parse the buffer and, if the parse is successful, it will jump back to the root to load the desired function. If the parse fails, the parser deposits an error number in the root and jumps to the entry SERLD in the root which loads the error overlay.

Ultimately the root will initiate another routine, either the error routine or the requested function.

#### 5. [Function routines]

These routines may further check the input and find errors. If errors are found, the function sets up the error routine and jumps to the root to load an error overlay. If it succeeds, the function will release the buffer and enter the root at the point where the root will reload the dispatcher.

#### 6. [Error Overlay]

The error overlay contains all error messages and the code needed to format the error message from the error number deposited in the root by the MCR component discovering the error.

## 7. [Final Exit]

The dispatcher calls the queue routine to obtain another buffer, if one is found the cycle of name table scanning resumes (starting at step 2). If no buffers are waiting, MCR exits.

#### 3.5 Partitions

The user area of RSX=11M is divided into partitions. In unmapped systems tasks are bound to a specific partition and must execute from that partition. In mapped systems tasks may be installed and subsequently executed in any partition provided the partition is large enough and sufficient checkpoint space is available in the task image.

A partition always consists of at least a main partition; the main partition can be subdivided into as many as seven subpartitions. The execution of tasks within the main partition and its subpartitions is mutually exclusive. This means that if a task is executing in the main partition no tasks may be executing in any subpartition of the main partition. Contrarywise, if a task is executing in a subpartition no task requiring the main partition may be executing. The subpartitions, however, can all execute in parallel.

Subpartitions exist so as to make it possible to reclaim and subdivide large partitions that service nonrealtime tasks like language translators.

If a main partition task is fixed in memory then no other main partition or subpartition task may execute until the task is unfixed. A fixed subpartition task will exclude the execution of a main partition task and other tasks wanting to execute from the subject subpartition. Other subpartitions operate independently.

An identical set of conditions apply to tasks that are not checkpointable.